# PW-82520/21N 3-PHASE DC MOTOR TORQUE CONTROLLER

#### **DESCRIPTION**

The PW-82520N (100Vdc) and PW-82521N (200Vdc) are high performance current regulating torque loop controllers designed to accurately regulate the current in the motor windings of 3-phase brushless DC and brush DC motors.

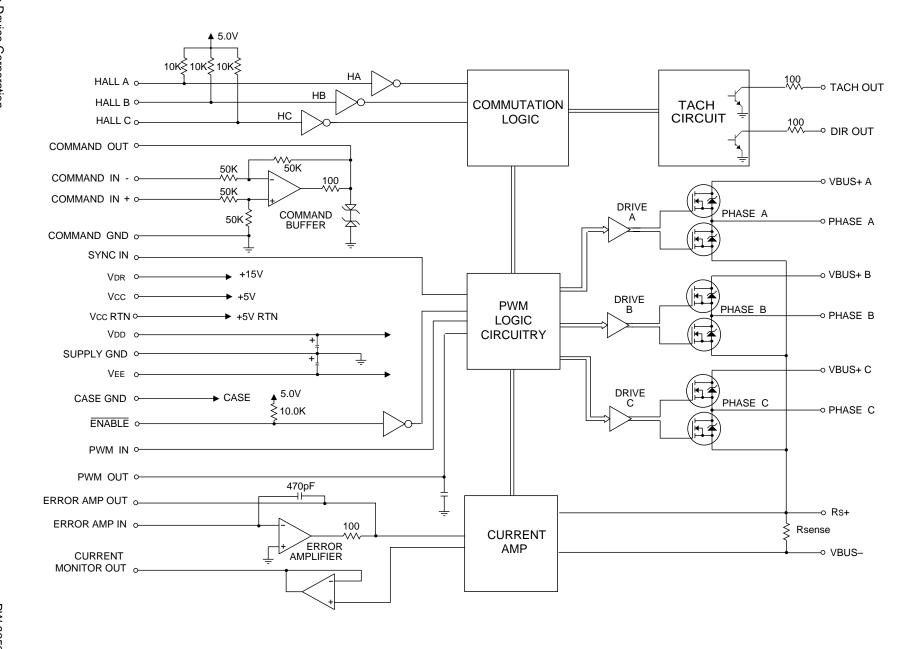

The PW-82520/21N is a completely self-contained motor controller that converts an analog input command signal into motor current and uses the signals from Hall-effect sensors in the motor to commutate the current in the motor windings. The motor current is internally sensed and processed into an analog signal. The current signal is summed together with the command signal to produce an error signal that controls the pulse width modulation (PWM) duty cycle of the output, thus controlling the motor current. The PW-82520/21N performance can be tuned by utilizing the internal error amplifier and the external Proportional/Integral (PI) regulator network components to match motor characteristics.

#### **APPLICATIONS**

The PW-82520/21N is ideal for applications requiring current regulation and/or holding torque at zero input command. System applications include: pumps, actuators, antenna position, environmental control, reaction/momentum wheel systems using brushless and brush motors, flight surface control on aircrafts for horizontal stabilizers and flaps, missile fin control, fuel and Hydraulic pumps, radar, and counter measure systems.

Packaged in a small DIP-style hybrid package, the PW-82520/21N is well suited for applications with limited printed circuit board area.

Data Device Corporation 105 Wilbur Place Bohemia, New York 11716 631-567-5600 Fax: 631-567-7358 www.ddc-web.com

### FEATURES

Self-Contained 3-Phase Motor Controller

Make sure the next Card you purchase

- Operates as Current or Voltage Controller

- 1, 3 or 10 Amp Output Current

- 1.5% Linearity

- 3% Current Regulating Accuracy

- User-Programmable Compensation

- 10 KHz 100 KHz PWM Frequency

- Complementary Four-Quadrant Operation

- Holding Torque through Zero Current

- Cycle-by-Cycle Current Limit

- Optional Radiation Tolerance to 100Krads (see PW-82520R data sheet)

FOR MORE INFORMATION CONTACT:

Technical Support: 1-800-DDC-5757 ext. 7677 or 7381

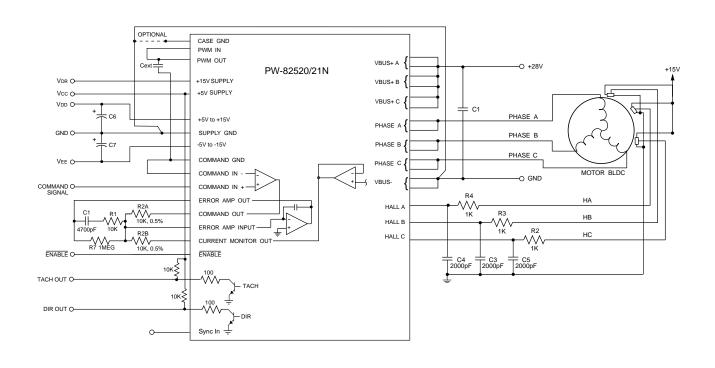

FIGURE 1. PW-82520/21N BLOCK DIAGRAM

| TABLE 1. PW-82520/21N ABSOLUTE MAXIMUM RATINGS (TC = +25°C UNLESS OTHERWISE SPECIFIED)   |                   |               |             |  |  |  |

|------------------------------------------------------------------------------------------|-------------------|---------------|-------------|--|--|--|

| PARAMETER                                                                                | SYMBOL            | VALUE         | UNITS       |  |  |  |

| BUS VOLTAGE PW-82520N / (PW-82521N)                                                      | VBUS+ A,B,C       | 100.0 (200.0) | Vdc         |  |  |  |

| -15V SUPPLY                                                                              | Vdr               | +17.5         | Vdc         |  |  |  |

| -5V TO +15V                                                                              | VDD               | +17.5         | Vdc         |  |  |  |

| -5V SUPPLY                                                                               | Vcc               | +5.5          | Vdc         |  |  |  |

| 5V TO -15V                                                                               | VEE               | -17.5         | Vdc         |  |  |  |

| /BUS- TO GND<br>Voltage Differential                                                     | Vgnddif           | 0-Vpb +1.0    | Vdc         |  |  |  |

| CONTINUOUS OUTPUT CURRENT PW-82520N1 PW-82520N3 PW-82520N0 / PW-82521N0                  | loc<br>loc<br>loc | 1<br>3<br>10  | A<br>A<br>A |  |  |  |

| PEAK OUTPUT CURRENT (PULSED t = 50μS) PW-82520N1 PW-82520N3 PW-82520N0 / PW-82521N0      | IOP<br>IOP<br>IOP | 3<br>8<br>18  | A<br>A<br>A |  |  |  |

| COMMAND INPUT +                                                                          | VCMD +            | ±15.0         | Vdc         |  |  |  |

| COMMAND INPUT -                                                                          | Vcmd -            | ±15.0         | Vdc         |  |  |  |

| _OGIC INPUTS:<br>ENABLE, SYNC IN, HA, HB, HC, ERROR AMP IN, PWM IN<br>FACH OUT / DIR OUT | VIH<br>Voh        | 7.0<br>40     | Vdc<br>Vdc  |  |  |  |

| TACH OUT / DIR OUT                                                                       | loL               | 20            | mA          |  |  |  |

### TABLE 2. PW-82520/21N SPECIFICATIONS (UNLESS OTHERWISE SPECIFIED, VBUS = 28VDC, VDR = +15V, VCC = +5V, VDD = +5V, VEE = -5V, TC = 25°C, LL = 500 $\mu$ H, PWM IN = PWM OUT AT $\frac{1}{2}$ FREE RUNNING FREQUENCY)

| PARAMETER                                                                                                                                                                    | SYMBOL                                          | TEST CONDITIONS                                                      | MIN          | TYP       | MAX                                                        | UNITS                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------|--------------|-----------|------------------------------------------------------------|----------------------------------|

| OUTPUT (PW-82520N1) Output Current Continuous Output Current Pulsed Current Limit Current Offset Output On-Resistance Output Conductor Resistance Diode Forward Voltage Drop | loc<br>lop<br>lcl<br>loffset<br>Ron<br>Rc<br>Vf | Pulse Width ≤ 50µsec  FIGURE 7, Vcmd = 0V +25°C +85°C +85°C ID = 1A  | 1.3<br>-20   | 1.5       | 1<br>3<br>1.8<br>+20<br>0.055<br>0.075<br>0.080<br>1.5     | A<br>A<br>A<br>mA<br>Ω<br>Ω<br>Ω |

| OUTPUT (PW-82520N3) Output Current Continuous Output Current Pulsed Current Limit Current Offset Output On-Resistance Output Conductor Resistance Diode Forward Voltage Drop | loc<br>lop<br>lcL<br>loffset<br>Ron<br>Rc<br>Vf | Pulse Width ≤ 50µsec  FIGURE 7, VcMD = 0V                            | 3.4<br>-20   | 4         | 3<br>8<br>4.5<br>+20<br>0.055<br>0.075<br>0.080<br>1.8     | A<br>A<br>A<br>mA<br>Ω<br>Ω<br>Ω |

| OUTPUT (PW-82520N0) Output Current Continuous Output Current Pulsed Current Limit Current Offset Output On-Resistance Output Conductor Resistance Diode Forward Voltage Drop | loc<br>lop<br>lcL<br>loffset<br>Ron<br>Rc<br>Vf | Pulse Width ≤ 50µsec  FIGURE 7, VcMD = 0V                            | 12.0<br>-100 | 14.0<br>0 | 10<br>18<br>15.4<br>+100<br>0.055<br>0.075<br>0.080<br>1.9 | A<br>A<br>A<br>mA<br>Ω<br>Ω<br>Ω |

| OUTPUT PW-82521N0 Output Current Continuous Output Current Pulsed Current Limit Current Offset Output On-Resistance Output Conductor Resistance Diode Forward Voltage Drop   | loc<br>lop<br>ICL<br>IOFFSET<br>RON<br>RC<br>VF | Pulse Width ≤ 50µsec  FIGURE 7, VcMD = 0V +25°C +85°C +85°C ID = 10A | 12.0<br>-0.3 | 14.0<br>0 | 10<br>18<br>15.4<br>+0.3<br>0.100<br>0.140<br>0.080<br>1.9 | A<br>A<br>A<br>Ω<br>Ω<br>Ω<br>V  |

## TABLE 2. PW-82520/21N SPECIFICATIONS (CONTINUED) (UNLESS OTHERWISE SPECIFIED, VBUS = 28VDC, VDR = +15V, VCC = +5V, VDD = +5V, VEE = -5V, TC = 25°C, LL = 500 $\mu$ H, PWM IN = PWM OUT AT ½ FREE RUNNING FREQUENCY)

| PARAMETER                                     | SYMBOL                                  | TEST CONDITIONS                              | MIN          | TYP          | MAX          | UNITS      |

|-----------------------------------------------|-----------------------------------------|----------------------------------------------|--------------|--------------|--------------|------------|

| PROPAGATION DELAY                             | Td (on)                                 | From 1.5V on ENABLE to                       |              | 40           |              | μs         |

|                                               | Td (aff)                                | 90% of <u>VBUS</u><br>From 3.5V on ENABLE to |              | 20           |              |            |

|                                               | Td (off)                                | 10% of VBUS                                  |              | ∠∪           |              | μs         |

| SWITCHING CHARACTERISTICS                     |                                         | 1070 51 1200                                 |              |              |              |            |

| PW-82520N1                                    |                                         |                                              |              |              |              |            |

| Upper Drive                                   |                                         | Rise Time =                                  |              |              |              |            |

| Turn-on Rise Time Turn-off Fall Time          | t <sub>r</sub>                          | 90% to 10% of VBUS<br>Fall Time =            |              | 75<br>30     |              | ns         |

| Lower Drive                                   | t <sub>f</sub>                          | 10% to 90% of VBUS                           |              | 30           |              | ns         |

| Turn-on Rise Time                             | t <sub>r</sub>                          | Io = 1A                                      |              | 50           |              | ns         |

| Turn-off Fall Time                            | ťf                                      |                                              |              | 60           |              | ns         |

| PW-82520N3                                    |                                         |                                              |              |              |              |            |

| Upper Drive Turn-on Rise Time                 |                                         | Rise Time = 90% to 10% of VBUS               |              | 150          |              | ne         |

| Turn-off Fall Time                            | t <sub>r</sub><br>t <sub>f</sub>        | Fall Time =                                  |              | 150          |              | ns<br>ns   |

| Lower Drive                                   | "                                       | 10% to 90% of V <sub>BUS</sub>               |              | 100          |              |            |

| Turn-on Rise Time                             | t <sub>r</sub>                          | Io = 3A                                      |              | 160          |              | ns         |

| Turn-off Fall Time                            | t <sub>f</sub>                          |                                              |              | 130          |              | ns         |

| PW-82520N0/21N0<br>Upper Drive                |                                         | Rise Time =                                  |              |              |              |            |

| Turn-on Rise Time                             | t <sub>r</sub>                          | 90% to 10% of VBUS                           |              | 200          |              | ns         |

| Turn-off Fall Time                            | t <sub>f</sub>                          | Fall Time =                                  |              | 200          |              | ns         |

| Lower Drive                                   | ·                                       | 10% to 90% of VBUS                           |              |              |              |            |

| Turn-on Rise Time Turn-off Fall Time          | t <sub>r</sub>                          | lo = 10A                                     |              | 200          |              | ns         |

| Tanti an Tani                                 | t <sub>f</sub>                          |                                              |              | 200          |              | ns         |

| CURRENT MONITOR AMP (ALL MODELS)              |                                         |                                              |              |              |              |            |

| Current Monitor Offset                        |                                         | loc = 0A                                     | -10          |              | +10          | mVdc       |

| Output Current                                |                                         |                                              | -10          |              | +10          | mA         |

| Output Resistance                             | Rout                                    |                                              |              |              | 1            | Ω          |

| CURRENT MONITOR AMP                           |                                         |                                              |              |              |              |            |

| (PW-82520N1) Current Monitor Gain             |                                         |                                              |              | 4            |              | V/A        |

|                                               |                                         |                                              |              | 4            |              | V/A        |

| CURRENT MONITOR AMP<br>(PW-82520N3)           |                                         |                                              |              |              |              |            |

| Current Monitor Gain                          |                                         |                                              |              | 1.33         |              | V/A        |

| CURRENT MONITOR AMP                           |                                         |                                              |              |              |              |            |

| (PW-82520/82521N0)                            |                                         |                                              |              |              |              |            |

| Current Monitor Gain                          |                                         |                                              |              | 0.40         |              | V/A        |

| CURRENT COMMAND                               |                                         | FIGURE 7                                     |              |              |              |            |

| Transconductance Ratio                        | G                                       |                                              |              |              |              |            |

| PW-82520N1                                    |                                         | lo = 1A                                      | 0.24         | 0.25         | 0.26         | A/V        |

| PW-82520N3<br>PW-82520/82521N0                |                                         | lo = 3A<br>lo = 10A                          | 0.73<br>2.37 | 0.75<br>2.50 | 0.76<br>2.63 | A/V<br>A/V |

| Non-Linearity                                 |                                         | IU = IUA                                     | -1.5         | 2.50         | 2.63<br>+1.5 | % FSR      |

| Temperature Coefficient of G                  |                                         |                                              | 1.0          |              |              |            |

| PW-82520N1/N3                                 |                                         |                                              |              | 0.038        |              | %FSR/°C    |

| PW-82520/82521N0                              |                                         |                                              |              | 0.05         |              | %FSR/°C    |

| VBUS+ SUPPLY                                  | \/\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |                                              |              |              |              |            |

| Nominal Operating Voltage<br>PW-82520N1/N3/N0 | Vnom                                    |                                              | 18           | 28           | 70           | Vdc        |

| PW-82521N0                                    |                                         |                                              | 36           | 56           | 140          | Vdc        |

| +15V SUPPLY                                   |                                         |                                              |              |              |              |            |

| Voltage                                       | Vdr                                     |                                              | +13.5        | +15.0        | +16.5        | Vdc        |

| Current                                       | Idr                                     | ENABLE = high                                |              | 100          |              | μA         |

| Current                                       | Inn                                     | ENABLE - low                                 |              | _            | 15           | m^         |

| N1<br>N3                                      | ldr<br>Idr                              | <u>ENABLE</u> = low<br>ENABLE = low          |              | 9<br>18      | 15<br>25     | mA<br>mA   |

| NO NO                                         | IDR                                     | ENABLE = low                                 |              | 30           | 45           | mA         |

|                                               | I                                       | <u> </u>                                     |              |              |              | l          |

## TABLE 2. PW-82520/21N SPECIFICATIONS (CONTINUED) (UNLESS OTHERWISE SPECIFIED, VBUS = 28VDC, VDR = +15V, VCC = +5V, VDD = +5V, VEE = -5V, TC = 25°C, LL = 500 $\mu$ H, PWM IN = PWM OUT AT ½ FREE RUNNING FREQUENCY)

| PVVIVI                                | IN = PVVIVI OUT A | 1 /2 FREE RUNNING F | REQUENC      | 1)        |             |             |

|---------------------------------------|-------------------|---------------------|--------------|-----------|-------------|-------------|

| PARAMETER                             | SYMBOL            | TEST CONDITIONS     | MIN          | TYP       | MAX         | UNITS       |

| +5V SUPPLY                            |                   |                     |              |           | Ì           |             |

| Voltage                               | Vcc               |                     | +4.5         | +5.0      | +5.5        | Vdc         |

| Current                               | Icc               |                     |              | 10        | 15          | mA          |

| +5V TO +15V SUPPLY                    |                   |                     |              |           |             |             |

| Voltage                               | VDD               | +15V                | +4.5         |           | +16.5       | Vdc         |

| Current                               | IDD               | +15V                |              | 35        | 50          | mA          |

| -5V TO -15V SUPPLY                    | .,                |                     | l            |           |             | l           |

| Voltage                               | VEE<br>IEE        | -15V<br>-15V        | -16.5        | 30        | -4.5<br>50  | Vdc<br>mA   |

| Current                               | IEE               | -15V                |              | 30        | 50          | mA          |

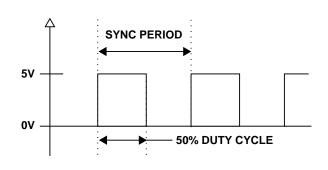

| SYNC IN<br>Low                        | VIL               |                     |              |           | 1.5         | Vdc         |

| High                                  | VIL               |                     | 3.5          |           | 1.5         | Vdc         |

| Duty Cycle                            | D.C.              |                     | 49           | 50        | 51          | %           |

| SYNC range as % of free-run frequency |                   |                     | 100          |           | 120         | %           |

| PWM IN                                |                   |                     | <u> </u>     |           |             |             |

| + Peak Voltage                        | Vp+               | Vcc = 4.5 - 5.5V    | 2.3          | 2.5       | 2.7         | V           |

| - Peak Voltage                        | Vp-               |                     | -2.7         | -2.5      | -2.3        | V           |

| Frequency                             | f <sub>PWM</sub>  |                     | 10           |           | 110         | KHz         |

| Linearity Error                       | LIN               |                     | -2           |           | +2          | %           |

| Duty Cycle                            | D.C.              |                     | 49           | 50        | 51          | %           |

| PWM OUT_                              | ,                 |                     |              |           |             |             |

| Free Run Frequency                    | f <sub>PWM</sub>  |                     | 0.5          | 400       | 105         |             |

| PW-82520N1/N3<br>PW-82520/82521N0     |                   |                     | 95<br>47.5   | 100<br>50 | 105<br>52.5 | KHz<br>KHz  |

| Stability, Temperature                |                   | Full Temp Range     | 47.5         | 0.5       | 2.0         | %           |

| HALL SIGNALS (HA, HB, HC)             |                   | T dir Temp Trange   | -            | 0.0       | 2.0         | /*          |

| Logic 0                               | VIL               |                     |              |           | 1.5         | Vdc         |

| Logic 1                               | VIH               |                     | 3.5          |           |             | Vdc         |

| ENABLE                                |                   |                     |              | <u> </u>  |             |             |

| Enabled                               | VIL               |                     |              |           | 1.5         | Vdc         |

| Disabled                              | VIH               |                     | 3.5          |           |             | Vdc         |

| TACH OUT/ DIR OUT                     |                   | Open Collector      | <u> </u>     |           |             | 1           |

| Current Sink                          | Vol               | <sup>'</sup> @ 1mA  |              | 0.7       | 1.2         | Vdc         |

| ISOLATION                             |                   |                     |              |           |             | İ           |

| Case to Ground                        |                   | 500 Vdc HIPOT       | 10           |           |             | MΩ          |

| COMMAND IN+/-                         |                   |                     | Ì            | İ         | Ì           | ĺ           |

| Differential Input                    | VCMD              |                     | -4           |           | +4          | Vdc         |

| Input Offset                          |                   |                     |              | _         | 800         | μV          |

| Input Offset Drift                    |                   |                     | ļ            | 2         | ļ           | μV/°C       |

| COMMAND OUT                           | V                 |                     | _            |           |             | ) //-I-     |

| Internal Voltage Clamp<br>Slew Rate   | VCLAMP            |                     | -5           | 3         | +5          | Vdc<br>V/µs |

| Settling Time                         | Vo = 0.2 to 4.5V  |                     |              | 1.4       |             | μs to 0.1%  |

| THERMAL (ALL MODELS)                  | 10 0.2 10 1.01    |                     |              |           | 1           | μο το σ,σ   |

| Junction Temperature                  | Tj                |                     |              |           | +150        | °C          |

| Case Operating Temperature            | Tc                |                     | -55          |           | +125        | °C          |

| Case Storage Temperature              | Tcs               |                     | -65          |           | +150        | °C          |

| THERMAL (PW-82520N1)                  |                   |                     |              |           |             |             |

| Thermal Resistance                    |                   |                     |              |           |             |             |

| Junction-Case                         | θj-c              |                     |              |           | 25          | °C/W        |

| Case-Air                              | θс-а              |                     |              |           | 10          | °C/W        |

| THERMAL (PW-82520N3)                  |                   |                     |              |           |             |             |

| Thermal Resistance Junction-Case      | 01.0              |                     |              |           | ١ ,         | l ∘c/w      |

| Case-Air                              | θj-c<br>θc-a      |                     |              |           | 9 10        | °C/W        |

| THERMAL (PW-82520N0/82521N0)          | - σσα             |                     | <del> </del> | -         | 10          | 5, **       |

| Thermal Resistance                    |                   |                     |              |           |             |             |

| Junction-Case                         | θј-с              |                     |              | 1         | 4           | °C/W        |

| Case-Air                              | θc-a              |                     |              |           | 5.5         | °C/W        |

| WEIGHT                                |                   |                     | 1            | 1         | †           | 1           |

| NO, N1, N3                            |                   |                     |              |           | 1.7 (48)    | oz (g)      |

| -1 -1                                 |                   |                     |              |           | I (,        | (9)         |

#### INTRODUCTION

The PW-82520/21N is a 3-phase high performance current control (torque loop) motor controller hybrid, which provides true four-quadrant control through zero current (Refer to FIGURE 1. PW-82520/21N Block Diagram). Its high Pulse Width Modulation (PWM) switching frequency makes it suitable for operation with low inductance motors. The PW-82520/21N hybrids can accept single-ended or differential mode command signals. The current gain can be easily programmed to match the end user system requirements. The addition of an externally wired compensation network provides the user with optimum control of a wide range of loads.

The PW-82520/21N uses single point current sense technology with an internal non-inductive hybrid sense resistor (Rsense), which yields a highly linear current output over the full -55°C to +125°C military temperature range. The output current non-linearity is less than 1.5% and the total error due to all the factors such as offset, initial component accuracy, etc., is maintained well below 3% of the full-scale rated output current.

The Hall sensor interface for current commutation has built-in decoder logic that ignores illegal codes and ensures that there is no cross conduction. The Hall sensor inputs are internally pulled up to +5V and they can be driven from open-collector outputs.

The PWM frequency can be programmed externally by adding a capacitor from PWM OUT to PWM GND. Multiple PW-82520N's can be synchronized in two ways: 1) by using one device as a master and connecting its PWM OUT pin to the PWM IN of all the other slave devices, or 2) by applying a master SYNC pulse from an external source to the PWM IN pins on all devices to be synchronized.

The ENABLE input signal provides quick start and shutdown of the internal PWM. In addition, built-in under-voltage fault protection turns off the output in case of improper power supply voltages. The hybrid features dual current limiting functions. The input command amplifier output is limited to ±5V, limiting the motor current under normal operation. In addition, there is a cycle-bycycle current limit which kicks in to protect the hybrid as well as the load (see TABLE 2 for IcL limits).

#### BASIC OPERATION AND ADVANTAGES

The PW-82520/21N uses a complementary four-quadrant drive technique to control current in the load. The complementary drive has the following advantages over standard drives:

- 1. Holding torque in the motor at zero commanded current

- 2. Linear current control through zero

- 3. No deadband at zero

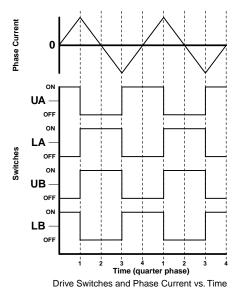

The complementary drive design produces a 50% PWM duty cycle in response to a zero current command. During a zero current command the benefit of a complementary 4 quadrant drive over a standard 4 quadrant is as follows:

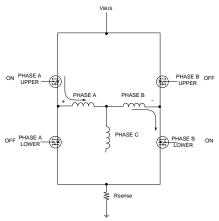

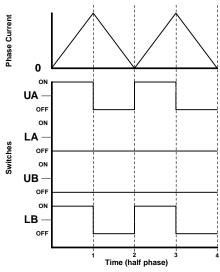

#### COMPLEMENTARY (FIGURES 2, 3A)

Complementary Drives produce a bi-directional holding torque by driving a balanced bi-polar current into the motor that has an average value of zero.

During the first quarter of the PWM cycle (starting at time zero on FIGURE 3A) the MOSFET's, PHASE A UPPER (UA) and PHASE B LOWER (LB) (FIGURE 2), are turned on. This allows current flow from phase A to phase B to increase to +Imax.

During the second quarter of the PWM cycle, the first pair of transistors, UA and LB are turned off and a second pair PHASE A LOWER (LA) & PHASE B UPPER (UB) (FIGURE 2) are turned on. This allows the current in phase A & B from the previous quarter cycle to decrease from Imax to zero. The average current during the first two-quarter cycles is positive.

During the third quarter of the PWM cycle, the second pair of switches UB & LA remain on allowing current to flow, in the negative direction, from phase B to phase A and increase to –Imax as shown in FIGURE 3A.

During the fourth quarter of the PWM cycle, the first pair of switches UA & LB are turned on while the second pair of switches UB & LA are turned off, to allow the current in the inductor to decrease to zero.

The average current in the phases for the third and fourth quarter cycles is negative.

The positive current (phase A to B) in the first two-quarter cycles produces a torque in one direction and the negative current (phase B to A) in the third and fourth quarter cycles produces a torque in the opposite direction. The average of the two opposing torques results in a net zero or holding torque.

FIRST HALF OF PWM CYCLE

FIGURE 3A. COMPLEMENTARY 4-QUADRANT DRIVE PWM CYCLE

#### NON-COMPLEMENTARY (FIGURES 2, 3B)

Non-Complementary Drives produce a unidirectional torque by applying a unipolar current into the motor that has an average positive value as shown in FIGURE 3B.

During the first half of the PWM cycle the MOSFET's, Phase A upper and Phase B lower, are turned on to provide current into the phases.

During the second half of the PWM cycle the drive is in dead time, all transistors are turned off, the motor current continues to flow in the same direction through the device diodes, until it decays to zero.

Current flowing in to and out of the phases produces a net torque in one direction.

#### MAJOR ADVANTAGES

The advantage of a complementary 4-quadrant drive over a standard 4-quadrant drive is that it provides holding torque during a zero current command. The motor current at 50% duty cycle is simply the magnetizing current of the motor winding. Using the complementary 4-quadrant technique allows the motor direction to be defined by the duty cycle.

Relative to a given switch pair, i.e. Phase A upper and Phase B lower, a duty cycle greater than 50% will result in a clockwise rotation whereas a duty cycle less than 50% will result in a counter clockwise rotation. Therefore, with the use of average current mode control, direction can be controlled without the use of a direction bit and the current can be controlled through zero in a very precise and linear fashion.

The PW-82520N contains all the circuitry required to close an average current mode control loop around a complementary 4-

Drive Switches and Phase Current vs. Time

### FIGURE 3B. STANDARD 4-QUADRANT DRIVE PWM CYCLE

quadrant drive. The PW-82520N use of average current mode control simplifies the control loop by eliminating the need for slope compensation and by eliminating the pole created by the motor inductance. Slope compensation and the pole created by the motor inductance are two limitations normally associated with implementing standard 4 quadrant current mode controls.

#### **FUNCTIONAL AND PIN DESCRIPTIONS**

#### VBUS+A, VBUS+B, VBUS+C

The VBUS+ supply is the power source for the motor phases. For the PW-82520 (PW-82521) series device, the normal operating voltage is 28Vdc (100Vdc) and may vary from +18 (+36) to +70Vdc (+140Vdc) with respect to VBUS-. The power-stage MOSFETs in the hybrid have an absolute maximum VBUS+ supply voltage rating of 100V (200V). The user must supply sufficient external capacitance or circuitry to prevent the bus supply from exceeding the maximum recommended voltages at the hybrid power terminals under any condition.

#### POWER-ON SEQUENCE (IMPORTANT!)

The VBUS+ should be applied at least 50ms after VDD and VEE to allow the internal analog circuitry to stabilize. If this is not possible, the hybrid must be powered up in the "disabled" mode.

#### **VBUS-**

This is the high current ground return for VBUS+. This point must be closely connected to SUPPLY GND for proper operation of the current loop.

#### VCC (+5V SUPPLY) AND VCC RTN

These inputs are used to power the digital circuitry of the hybrid.

#### VDR (+15V SUPPLY)

This input is used to power the gate driver circuitry for the output MOSFETs. There is no power consumption from VDR when the hybrid is disabled.

#### VDD (+5V TO +15V SUPPLY), VEE (-5V TO -15V SUPPLY)

These inputs can vary from  $\pm 5V$  to  $\pm 15V$  as long as they are symmetrical. VDD and VEE are used to power the small signal analog circuitry of the hybrid. Please note that using  $\pm 5V$  supply will reduce the quiescent power consumption by approximately 60% when compared to  $\pm 15V$  operation.

#### **SUPPLY GND**

This pin is the return for the VDR, VEE, VDD supplies. The phase current sensing technique of the PW-82520N/21N requires that VBUS- and SUPPLY GND (see FIGURES 6 and 7) be connected together externally (see VBUS- supply).

#### CASE GND

This pin is internally connected to the hybrid case. In some applications the user may want to tie this to Ground for EMI considerations.

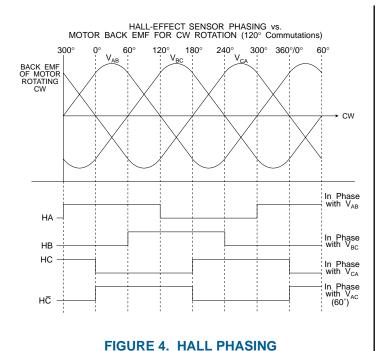

#### HALL A, B, C SIGNALS

These are logic signals from the motor Hall-effect sensors. They use a phasing convention referred to as 120 degree spacing; that is, the output of HA is in phase with motor back EMF voltage VAB, HB is in phase VBC, and HC is in phase with VCA. Logic

"1" (or HIGH) is defined by an input greater than 3.5Vdc or an open circuit to the controller; Logic "0" (or LOW) is defined as any Hall voltage input less than 1.5Vdc. Internal to the PW-82520/21N are 10K pull-up resistors tied to +5Vdc on each Hall input.

The PW-82520/21N will alternately operate with Hall phasing of 60° electrical spacing. If 60° commutation is used, then the output of HC must be inverted as shown in FIGURES 4 and 5. FIGURE 4 illustrates the Hall sensor outputs along with the corresponding back emf voltage they are in phase with.

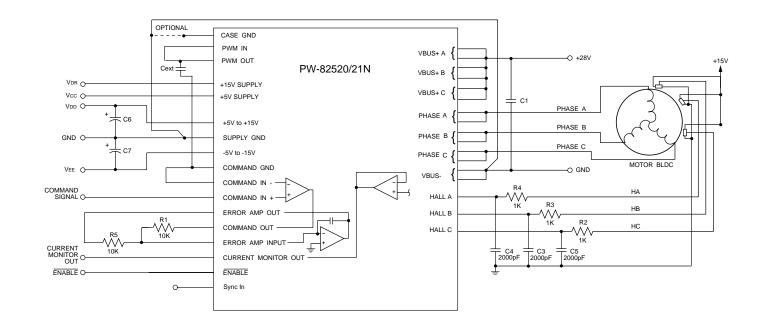

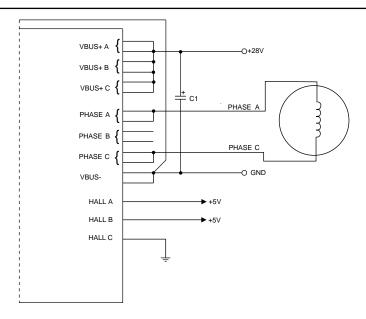

#### HALL INPUT SIGNAL CONDITIONING

When the motor is located more than two feet away from the PW-82520/21N controller or is in a noisy electrical environment the Hall inputs require filtering from noise. It is recommended to use a 1K $\Omega$  resistor in series with the Hall signal and a 2000 pF capacitor from the Hall input pin to the Hall supply ground pin as shown in FIGURES 6 and 7.

#### PHASE A, B, C

These are the power drive outputs to the motor and switch between VBUS+ Input and VBUS- Input or become high impedance (see TABLE 3).

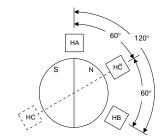

120° S N 120°

F POSITION SENSOR (HALL) SPACIN

REMOTE POSITION SENSOR (HALL) SPACING FOR 120 DEGREE COMMUTATION

REMOTE POSITION SENSOR (HALL) SPACING FOR 60 DEGREE COMMUTATION

FIGURE 5. HALL SENSOR SPACING

FIGURE 6. VOLTAGE CONTROL HOOK-UP

FIGURE 7. TORQUE (CURRENT) CONTROL HOOK-UP

#### **ENABLE**

The ENABLE input is an active low (L) logic signal that enables or disables the internal PWM. In the disable mode (H), the PWM is shut down and the outputs, Phase A, Phase B and Phase C, are in an "off" state and no voltage is applied to the motor.

#### TACH OUT

The TACH OUT provides a tachometer signal that is a square wave with a frequency relative to motor speed and is derived from the three Hall inputs HA, HB, HC. The tachometer circuitry combines these three signals into a single pulse train as a 50%-duty-cycle pulse. There are three pulses that occur every 360 electrical degree. The number of pulses per motor revolution is formulated below:

$$Pr = \frac{P}{2} \times 3$$

(e.g., 6 pulses/revolution for a 4 pole motor)

The motor RPM is:

$$RPM = \frac{Tf \times 60}{Pr}$$

where:

P = number of motor poles

Pr = number of pulses per revolution

Tf = Tach output frequency cycles/second

#### **DIR OUT**

The DIR OUT indicates the direction the motor is rotating, clockwise (CW) for a HI (open collector), or counterclockwise (CCW), indicated as a logic LOW (ground).

#### **CURRENT MONITOR OUT**

This is a bipolar analog output voltage representative of motor current. The CURRENT MONITOR OUT will have the same scaling as the COMMAND IN inputs.

#### SYNC IN

This input, as shown in FIGURE 9, is used to synchronize the PWM switching frequency with an external clocking device. The PWM switching frequency can be pulled to up-to 20% faster than its free running frequency.

#### **PWM IN**

The PWM comparator inputs are used to control the PWM pulse width. PWM out or an external triangular waveform is connected to this pin.

**WARNING:** Never apply power to the hybrid without connecting either PWM OUT or an external triangular waveform to PWM IN! Failure to do so may result in one or more outputs latching on.

#### PWM FREQUENCY

The PWM frequency from the PW-82520N1/N3 (PW-82520N0/21N0) PWM OUT pin will free-run at a frequency of 100KHz ± 5KHz (50KHz ± 2.5KHz). The PWM frequency is user adjustable from 100KHz (50KHz) down to 10KHz through the addition of an external capacitor. The PWM triangular waveform generated internally is brought out to the PWM OUT pin. This output, or an external triangular waveform generated by the user, may be connected to PWM IN on the hybrid.

#### **PWM OUT**

This is the output of the internally generated PWM triangle waveform. It is normally connected to PWM IN. The frequency of this output may be lowered by connecting an NPO capacitor (Cext) between PWM OUT and COMMAND GND. The PWM frequency is determined by the following formula:

PW-82520N1/N3: PW-82520/21N0:

33.0E-6 16.5E-6 330pF + CextpF 330pF + CextpF

#### ERROR AMP INPUT, ERROR AMP OUT

These are the input and output pins for the error amplifier and are used for compensation.

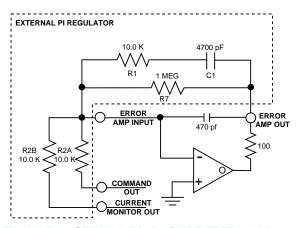

FIGURE 8. STANDARD PI CURRENT LOOP

FIGURE 9. SYNC INPUT SIGNAL

#### COMPENSATION

The PI regulator in the PW-82520/21N can be tuned to a specific load for optimum performance. FIGURE 8 shows the standard current loop configuration and tuning components. By adjusting R1, R2 and C1, the amplifier can be tuned. The value of R1, C1 will vary, depending on the loop bandwidth requirement.

#### COMMAND IN+. COMMAND IN-. COMMAND GROUND, COMMAND OUT

These are the connection pins for the command amplifier. The command amplifier has a differential input that operates from a ±4Vdc full-scale analog current command. The command amplifier output signal is internally limited to approximately ±5Vdc to prevent the amplifier from saturating. The input impedance of the command amplifier is  $50K\Omega$ .

The PW-82520/21N can be used either as a current or voltage mode controller. When used as a torque controller (current mode), the input command signal is processed through the command buffer, which is internally limited to ±5Vdc. The output of the buffer (command out) is summed with the current monitor output into the error amplifier. External compensation is used on the error amp, so the response time can be adjusted to meet the application.

When used in the voltage mode, the voltage command signal is applied to the command amplifier, to control the voltage applied to the motor. The command amplifier output is coupled into the error amplifier. The error amplifier directly varies the PWM duty cycle to control the voltage applied to the motor phase. The nominal PWM frequency in the voltage mode is 50% with zero volts applied to the command input. The PWM duty cycle is varied by the voltage applied to the command input according to the transfer function, 12% per volt applied to the command input. The

| TABLE 3. COMMUTATION TRUTH TABLE |      |    |    |         |            |            |            |

|----------------------------------|------|----|----|---------|------------|------------|------------|

|                                  | INPU | TS |    | OUTPUTS |            |            |            |

| ENABLE                           | DIR* | НА | нв | нс      | PHASE<br>A | PHASE<br>B | PHASE<br>C |

| L                                | CW   | 1  | 0  | 0       | Н          | L          | Z          |

| L                                | CW   | 1  | 1  | 0       | Н          | Z          | L          |

| L                                | CW   | 0  | 1  | 0       | Z          | Н          | L          |

| L                                | CW   | 0  | 1  | 1       | L          | Н          | Z          |

| L                                | CW   | 0  | 0  | 1       | L          | Z          | Н          |

| L                                | CW   | 1  | 0  | 1       | Z          | L          | Н          |

| L                                | CCW  | 1  | 0  | 1       | Z          | Н          | L          |

| L                                | CCW  | 0  | 0  | 1       | Н          | Z          | L          |

| L                                | CCW  | 0  | 1  | 1       | Н          | L          | Z          |

| L                                | CCW  | 0  | 1  | 0       | Z          | L          | Н          |

| L                                | CCW  | 1  | 1  | 0       | L          | Z          | Н          |

| L                                | CCW  | 1  | 0  | 0       | L          | Н          | Z          |

| Н                                | -    | -  | -  | -       | Z          | Z          | Z          |

<sup>1=</sup>Logic Voltage >3.5Vdc, 0=Logic voltage < 1.5Vdc DIR is based on the convention shown in FIGURE 4

Actual motor set up might be different.

duty cycle range of the output voltage is limited to approximately 5-95% in both current and voltage modes.

#### COMMAND GND

This pin is used when the command buffer is used single-ended and the COMMAND IN- or COMMAND IN+ are tied to COMMAND GND.

#### TRANSCONDUCTANCE RATIO AND OFFSET

When the PW-82520/21N is used in the current mode, the command inputs (COMMAND IN+ and COMMAND IN-) are designed such that ±4Vdc on either input, with the other input connected to ground will result in ± full-scale current (Continuous Output Current: (loc) - Refer to TABLE 2) flow into the load. The dc current transfer ratio accuracy is ±5% of the rated current including offset and initial component accuracy. The initial output dc current offset with both COMMAND IN+ and COMMAND IN- tied to the ground will be as shown in TABLE 2 (loffset) when measured using a load of 0.5mH and 1.0W at ambient room temperature with standard current loop compensation (see FIGURE 8). The winding phase current error shall be within the cumulative limits of the transconductance ratio error and the offset error.

#### Rs+

Rs+ is the high side of the sense resistor used for non-scaled test purposes only. Accuracy is not a guaranteed parameter.

#### **OUTPUT CURRENT**

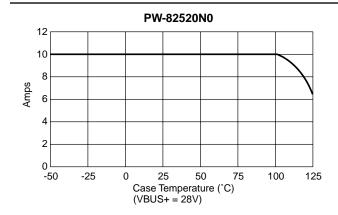

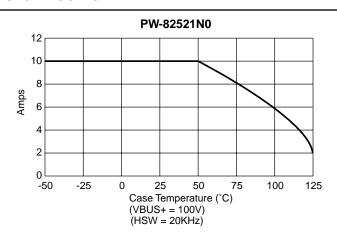

Output current derating as a function of the hybrid case temperature is provided in FIGURES 11 and 12. The hybrid contains internal pulse by pulse current limit circuitry to limit the output current during fault conditions (See TABLE 2). Current Limit accuracy is +10/-15%.

WARNING! The PW-82520/(21)N does not have short circuit protection. The PW-82520/(21)N must see a minimum of 100μH (400μH) inductive load phase-to-phase or enough phase-to-phase line-to-line resistance to limit the continuous output current to less than loc at all times. Operation into a short or a condition that requires excessive output current will damage the hybrid.

| TABLE 4. HALL INPUTS FOR<br>H-BRIDGE CONTROLLER |            |    |    |    |              |   |   |  |

|-------------------------------------------------|------------|----|----|----|--------------|---|---|--|

| INPUTS OUTPUTS                                  |            |    |    |    |              |   |   |  |

| ENABLE                                          | COMMAND IN | НА | НВ | нс | C PHA PHB PH |   |   |  |

| L                                               | Positive   | 1  | 1  | 0  | Н            | Z | L |  |

| L                                               | Negative   | 1  | 1  | 0  | L            | Z | Н |  |

| Н                                               | -          | 1  | 1  | 0  | Z            | Z | Z |  |

#### THERMAL OPERATION

It is necessary that the base (heat sink surface - FIGURE 13) of the PW-82520/21N be mounted to a heat sink. This heat sink shall have the capacity to dissipate heat generated by the hybrid at all levels of current output, up to the peak limit, while maintaining the case temperature limit as per FIGURE 11.

#### **BRUSH MOTOR OPERATION**

The PW-82520/21N can also be used as a brush motor controller for current or voltage control in an H-Bridge configuration. The PW-82520/21N would be connected as shown in FIGURE 10.

All other connections are as shown in either FIGURES 6 or 7 depending on voltage or current mode operation. The Hall inputs are wired per TABLE 4. A positive input command will result in positive current to the motor out of Phase A.

#### **OPTIONAL FEATURES**

#### EXTERNAL SENSING RESISTOR

An external sense resistor can be connected to replace the internal resistor if this option is required. Please contact factory for this option.

FIGURE 10. BRUSH MOTOR HOOK-UP

FIGURE 11. OUTPUT CURRENT FOR CONTINUOUS COMMUTATION (ELECTRICAL > 600RPM, PWM = 50KHZ)

#### PW-82520/21N POWER DISSIPATION

There are two major contributors to power dissipation in the motor driver: conduction losses, and switching losses.

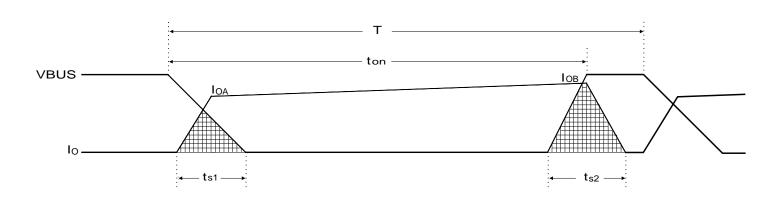

#### An example calculation is shown below:

VBUS = +28 V (Bus Voltage)

IOA = 3 A, IOB = 7 A (see FIGURE 12)

f<sub>PWM</sub> = 25 KHz (switching frequency)

ton = 36  $\mu$ s, T = 40  $\mu$ s (90% duty cycle) (see FIGURE 12)

Ron =  $0.055 \Omega$  (on-resistance, see TABLE 2)

$Rc = 0.080 \Omega$  (conductor resistance, see TABLE 2)

ts1 = tf = 200 ns, ts2 = 2tr = 400 ns (see TABLE 2, FIGURE 12)

Imotor rms =

$$\sqrt{\left(IOBIOA + \frac{(IOB - IOA)^2}{3}\right) \left(\frac{ton}{T}\right)}$$

Imotor rms =

$$\sqrt{\left(7 \times 3 + \frac{(7 - 3)^{2}}{3}\right)\left(\frac{36}{40}\right)}$$

I<sub>motor rms</sub>= 4.87 amps

#### 1. TRANSISTOR CONDUCTION LOSSES (PT)

$PT = (Imotor rms)^2 x (Ron)$

$PT = (4.87)^2 \times (0.055)$

PT = 1.30 Watts

#### 2. SWITCHING LOSSES (Ps)

Ps = [VBUS (IOA (ts1) + IOB (ts2)) fo]/2

Ps =  $[28 (3 (200 x10^{-9}) + 7 (400 x10^{-9})) 25x10^{3}]/2$

Ps = 1.19 Watts

#### TRANSISTOR POWER DISSIPATION ( PQ )

Pq = PT + Ps

Pq = 1.30 + 1.19 = 2.49 Watts

#### **OUTPUT CONDUCTOR DISSIPATION**

$Pc = (Imotor rms)^2 x (Rc)$

$Pc = (4.87)^2 \times (0.080)$

Pc = 1.90 Watts

### 3. TRANSISTOR POWER DISSIPATION FOR CONTINUOUS COMMUTATION (ELECTRICAL > 600RPM)

Pqc = Pq (0.33)

$Pqc = (2.49) \times (0.33)$

Pqc = 0.82 Watts

#### 4. TOTAL HYBRID POWER DISSIPATION

$PTOTAL = (Pq + Pc) \times 2$

$PTOTAL = (2.49 + 1.90) \times 2$

PTOTAL = 8.78 Watts

#### FIGURE 12. OUTPUT CHARACTERISTICS

| TABLE 5. PW-82520/21N PIN FUNC-<br>TIONS |          |     |                          |  |  |  |  |

|------------------------------------------|----------|-----|--------------------------|--|--|--|--|

| PIN                                      | FUNCTION | PIN | FUNCTION                 |  |  |  |  |

| 1                                        | VBUS+ A  | 41  | TACH OUT                 |  |  |  |  |

| 2                                        | VBUS+ A  | 40  | DIR OUT                  |  |  |  |  |

| 3                                        | PHASE A  | 39  | HALL C                   |  |  |  |  |

| 4                                        | PHASE A  | 38  | HALL B                   |  |  |  |  |

| 5                                        | VBUS+ B  | 37  | HALL A                   |  |  |  |  |

| 6                                        | VBUS+ B  | 36  | ENABLE                   |  |  |  |  |

| 7                                        | PHASE B  | 35  | Vcc                      |  |  |  |  |

| 8                                        | PHASE B  | 34  | Vcc RTN                  |  |  |  |  |

| 9                                        | VBUS-    | 33  | Vdr                      |  |  |  |  |

| 10                                       | VBUS-    | 32  | SYNC IN                  |  |  |  |  |

| 11                                       | RS+      | 31  | Vdd                      |  |  |  |  |

| 12                                       | RS+      | 30  | SUPPLY GND               |  |  |  |  |

| 13                                       | VBUS+ C  | 29  | VEE                      |  |  |  |  |

| 14                                       | VBUS+ C  | 28  | N/C                      |  |  |  |  |

| 15                                       | PHASE C  | 27  | N/C                      |  |  |  |  |

| 16                                       | PHASE C  | 26  | CURRENT MONI-<br>TOR OUT |  |  |  |  |

|                                          |          | 25  | ERROR AMP IN             |  |  |  |  |

|                                          |          | 24  | ERROR AMP OUT            |  |  |  |  |

|                                          |          | 23  | COMMAND OUT              |  |  |  |  |

|                                          |          | 22  | COMMAND IN -             |  |  |  |  |

|                                          |          | 21  | COMMAND IN +             |  |  |  |  |

|                                          |          | 20  | COMMAND GND              |  |  |  |  |

|                                          |          | 19  | PWM OUT                  |  |  |  |  |

|                                          |          | 18  | PWM IN                   |  |  |  |  |

|                                          |          | 17  | CASE GND                 |  |  |  |  |

<sup>\*</sup> N/C pins have internal connections for factory test purposes.

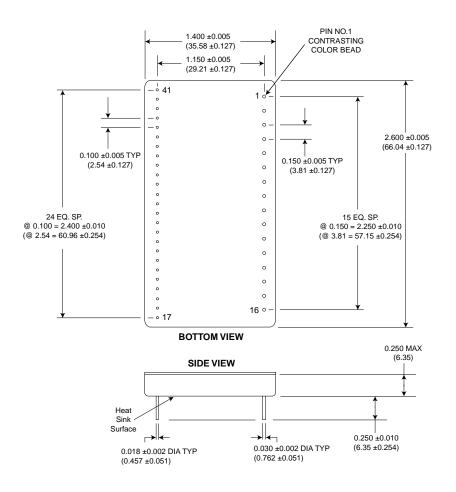

#### NOTES:

- 1. DIMENSIONS IN INCHES (MM). 2. LEAD IDENTIFICATION NUMBERS ARE FOR REFERENCE ONLY.

FIGURE 13. MECHANICAL OUTLINE

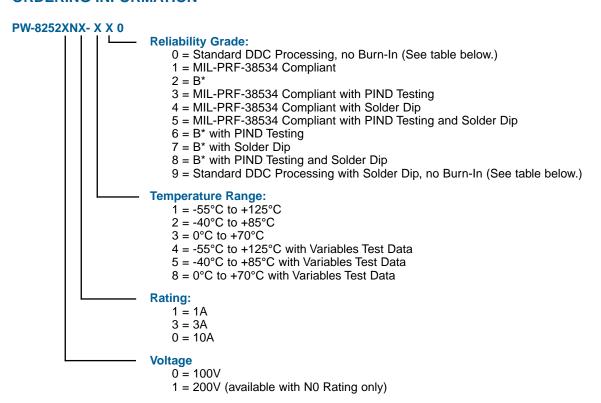

#### **ORDERING INFORMATION**

<sup>\*</sup>Standard DDC Processing with burn-in and full temperature test — see table below.

| STANDARD DDC PROCESSING |                            |              |  |  |  |  |

|-------------------------|----------------------------|--------------|--|--|--|--|

| TEST                    | MIL-STD-883                |              |  |  |  |  |

| 1231                    | METHOD(S)                  | CONDITION(S) |  |  |  |  |

| INSPECTION              | 2009, 2010, 2017, and 2032 | _            |  |  |  |  |

| SEAL                    | 1014                       | A and C      |  |  |  |  |

| TEMPERATURE CYCLE       | 1010                       | С            |  |  |  |  |

| CONSTANT ACCELERATION   | 2001                       | А            |  |  |  |  |

| BURN-IN                 | 1015, TABLE 1              |              |  |  |  |  |

The information in this data sheet is believed to be accurate; however, no responsibility is assumed by Data Device Corporation for its use, and no license or rights are granted by implication or otherwise in connection therewith.

Specifications are subject to change without notice.

105 Wilbur Place, Bohemia, New York, U.S.A. 11716-2482

For Technical Support - 1-800-DDC-5757 ext. 7677 or 7381

Headquarters, N.Y., U.S.A. - Tel: (631) 567-5600, Fax: (631) 567-7358 Southeast, U.S.A. - Tel: (703) 450-7900, Fax: (703) 450-6610 West Coast, U.S.A. - Tel: (714) 895-9777, Fax: (714) 895-4988 United Kingdom - Tel: +44-(0)1635-811140, Fax: +44-(0)1635-32264 Ireland - Tel: +353-21-341065, Fax: +353-21-341568 France - Tel: +33-(0)1-41-16-3424, Fax: +33-(0)1-41-16-3425 Germany - Tel: +49-(0)8141-349-087, Fax: +49-(0)8141-349-089 Japan - Tel: +81-(0)3-3814-7688, Fax: +81-(0)3-3814-7689 World Wide Web - http://www.ddc-web.com